# **Improving Equipment Clocks**

- < Equipment Clocks

- < Overall clock improvements

- Content of the second secon

- Improvement possibilities

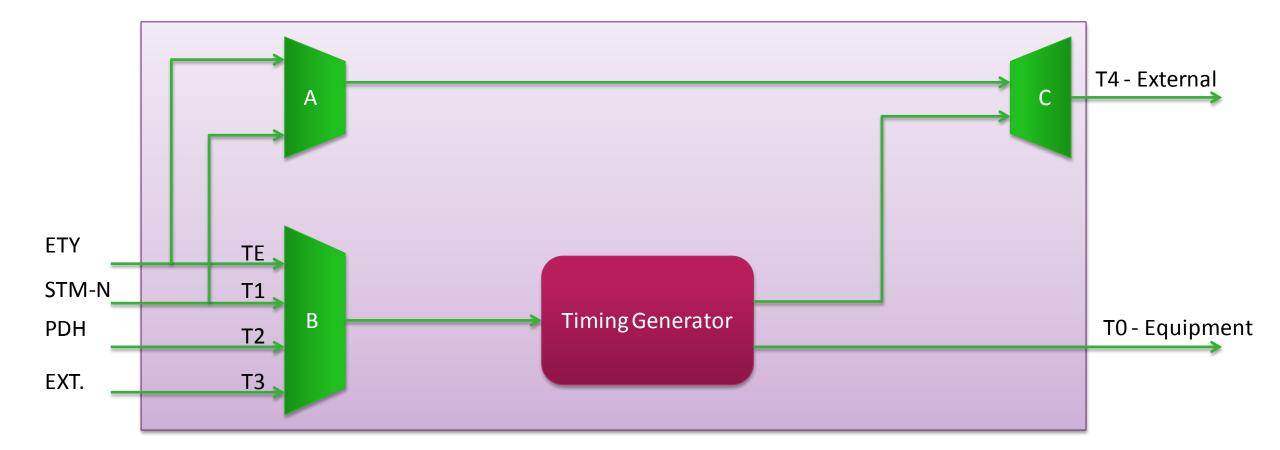

#### <sup>2</sup> Equipment Clock blocks

G.8264-Y.1364 (14) \_FA.2

# 3 Equipment Clocks

**G**.813

SDH Slave Equipment Clock

**G.8262**

Certain Contract C

Ethernet Equipment Clock

Option 1 – Based on E1 Hierarchy of Networks (Europe and Asia) Option 2 – Based on T1 Hierarchy of Networks (North America)

G.8263 defines Packet Equipment Clock - Frequency

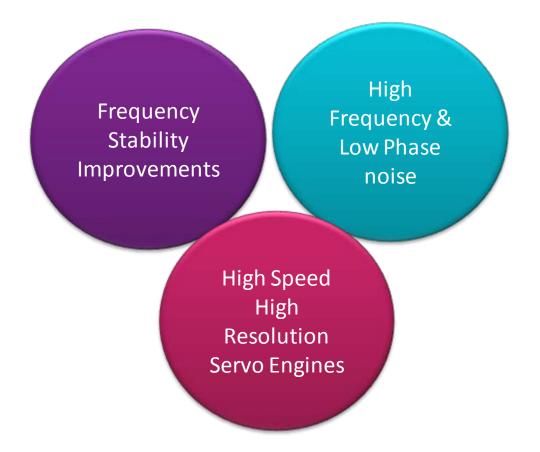

## Improvement in Reference Clocks & Servos

# rakon

Technology Improvements bring superior performance at the same cost

rakon

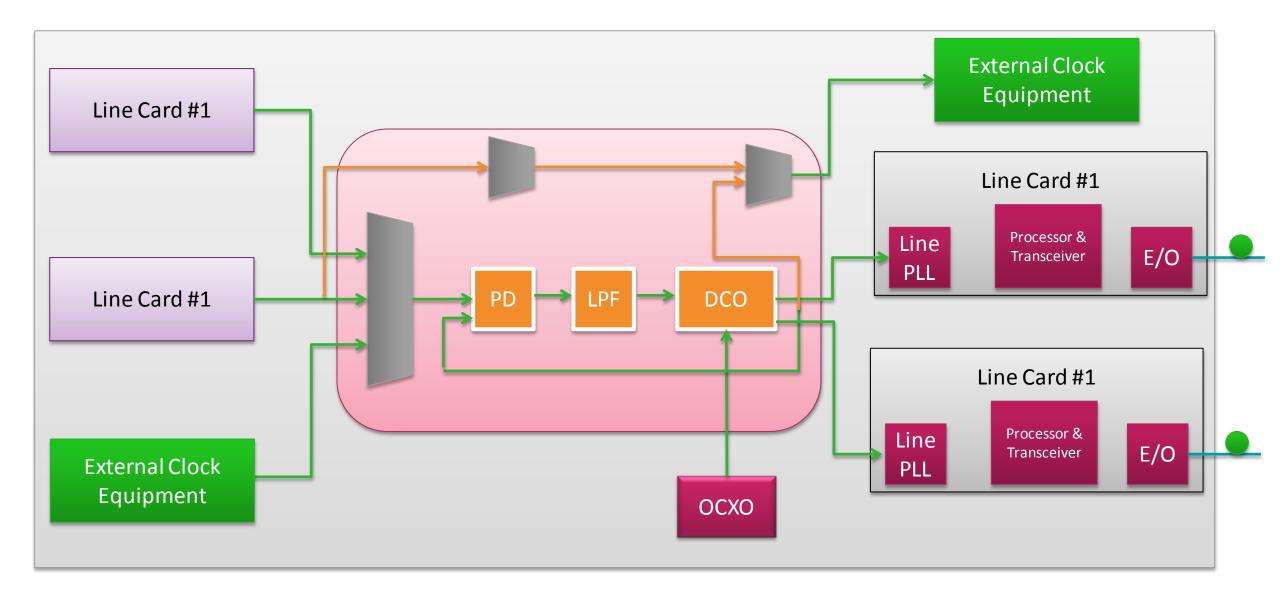

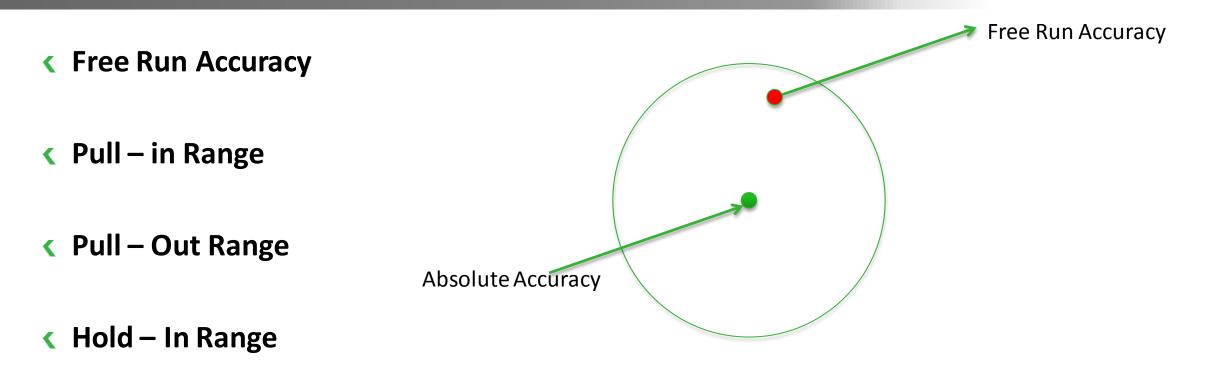

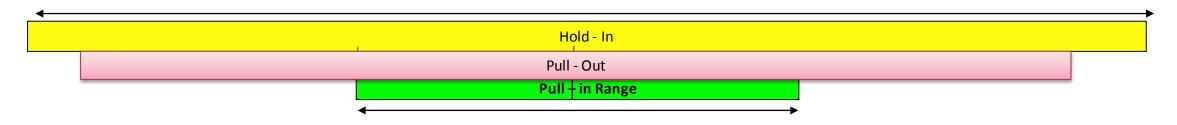

#### General Clock Architectures

#### Basic Features – Improvements?

rakon

# Noise – Jitter – Improvements?

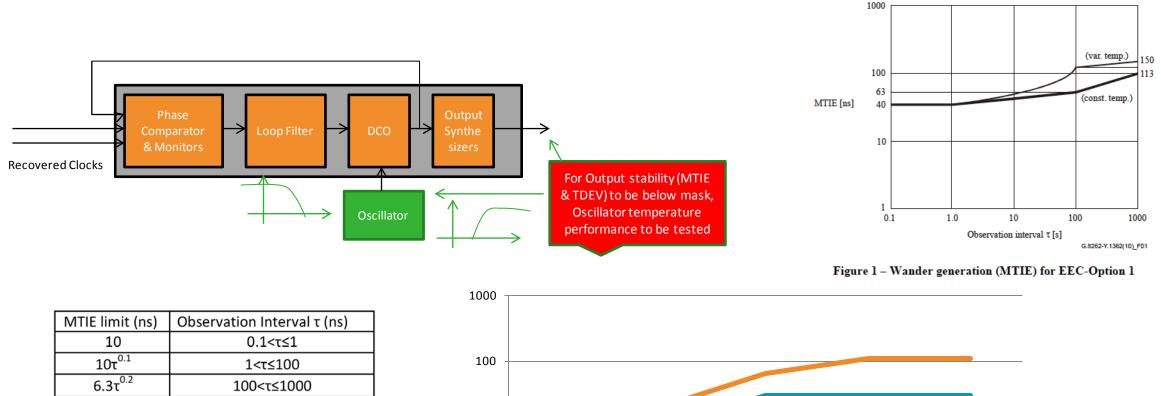

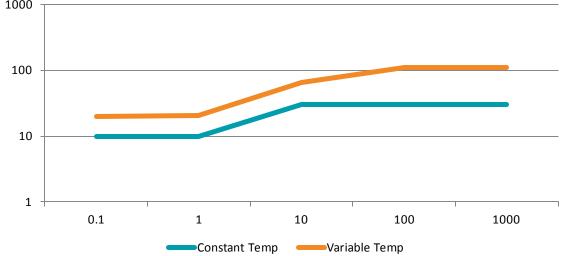

#### Wander Generation

Temeperatuer effects

| 0.5τ | τ≤100 |  |

|------|-------|--|

| 50   | τ>100 |  |

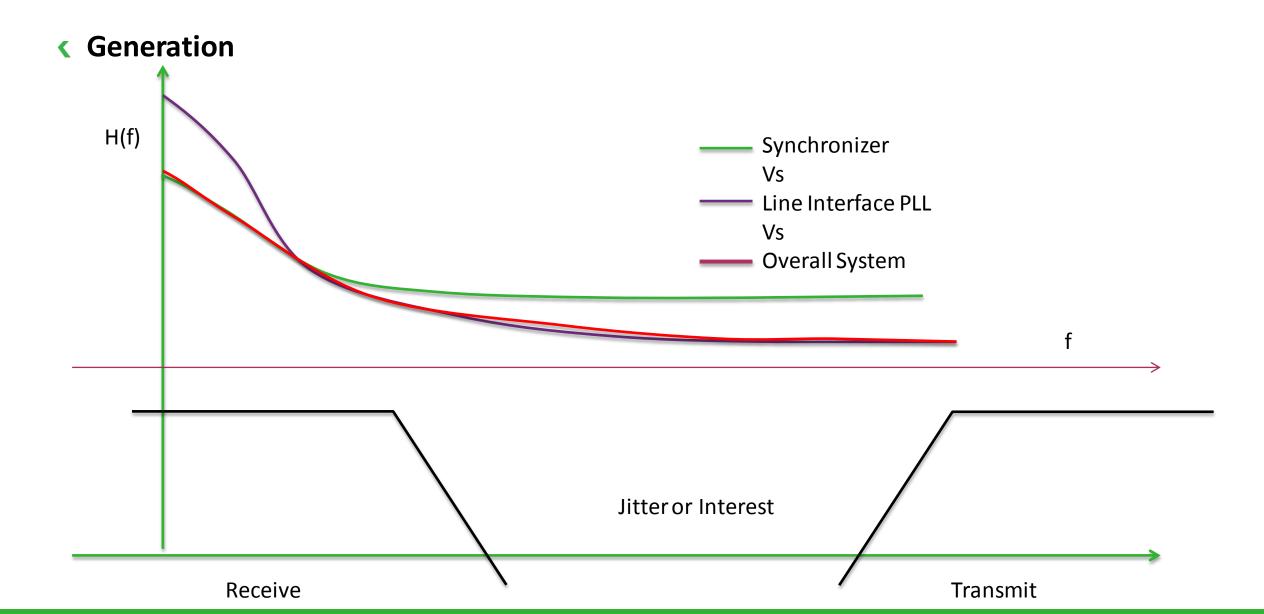

# Noise Transfer – Improvements?

#### **Loop bandwidth Recommendations**

- □ 1-10 Hz for Option 1

- □ 0.1Hz for Option 2

- □ ~ 1mHz for G.8263

- □ 0.05-0.1Hz for G.8273.2/G.8273.2

#### K Harmonize to Packet Clocks

□ 0.05Hz to 0.1Hz for all applications

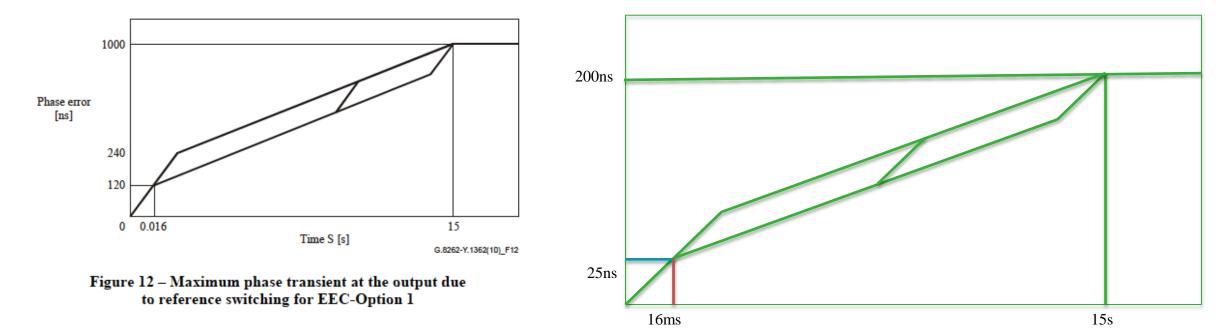

## Short Term phase transient response

#### Keference Switching or Input interruptions

Entry to holdover – 25ns Max each for two possible transitions Max phase slope for entry to holdover – 1.6ppm >16ms, upto 15 seconds – 10ppb phase error

rakon

Max phase error – 200ns

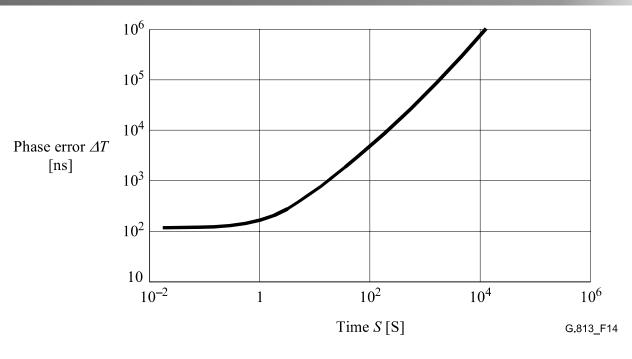

# **Long Term Holdover**

$\Delta T(S) = \{ (a_1 + a_2) S + 0.5 b S^2 + c \} \text{ [ns]}$

where:

$$a_1 = 50 \text{ ns/s} \text{ (see Note 1)};$$

$a_2 = 2000 \text{ ns/s} \text{ (see Note 2)};$

$b = 1.16 \times 10^{-4} \text{ ns/s}^2 \text{ (see Note 3)};$

$c = 120 \text{ ns} \text{ (see Note 4)}.$

| ltem | Description            | Units   | Option 1                | Option 2 | Proposal                |

|------|------------------------|---------|-------------------------|----------|-------------------------|

| S    | Duration               | Seconds | S>15                    | TBD      | 1 year                  |

| a1   | Initial Accuracy       | ns/s    | 50                      | 50       | 1                       |

| a2   | Temperature Effects    | Ns/s    | 2000                    | 300      | 100                     |

| b    | Oscillator ageing      | ns/s2   | 1.16E-04<br>(10ppb/day) | 4.63E-04 | 1.16E-04<br>(10ppb/day) |

| С    | Entry/Exit phase error | ns      | 120                     | 1000     | 25                      |

| d    | Drift                  | ns/s2   | -                       | 4.63E-04 | -                       |

# Critical Improvements

#### Temperature stability

- Improved algorithms and thermal designs

- Cost impact

#### Temperature slope

Quality crystals, improved test equipment

#### < Ageing

Improved crystals

#### PLLs with fine resolution controls

Output phase movements <1ppt</p>

#### < Integration

Digital interfaces, Smart compensation

# <sup>14</sup> Summary

- With advancement in Oscillator and PLL technologies, significant performance improvement on equipment clocks possible

- Significant performance Improvements are possible on

- Wander generation

- Short term phase transient response

- Long term holdover

- Phase response to input signal interruptions

- Phase discontinuity